A lot has been said about slots in ground planes when it comes to EMC/EMI. There are some good resources on the reasons why you should avoid having any slots in your PCB planes if you can, I’ll link some of them at the end of this post.

So why am I writing yet another article on ground plane slots? Ignoring the fact that a lot of them are clearly using our friend GPT and are just plain copies of each other, there is not enough awareness that this seemingly small detail in your PCB layout can have such an impact on your emissions, radiated and conducted.

This is also a good use case for electromagnetic simulation, which to some degree, I think should be part of any EMC engineer’s toolset.

I’m not expecting anyone to become proficient in numerical methods but as you will see, EM simulation can give you some insights that would be nearly impossible to measure on a physical PCB.

First, let’s revisit some electromagnetic theory:

Return Path? Ah?

It’s very easy to forget that, for any signal trace, there is a corresponding return current associated with it and that return current will have to flow either through a dedicated path (ideally under your signal trace, as we will see) or in the worst case, through air gaps (displacement currents, this is one of your archenemies in EMC/EMI)

Here’s a (very) simplified trace:

The red lines represent current. As you can see, the return current flows underneath the trace and this is all fine unless that return path under the trace is missing or far away.

So what happens to this return current if we have any gaps under the trace?

Let me illustrate:

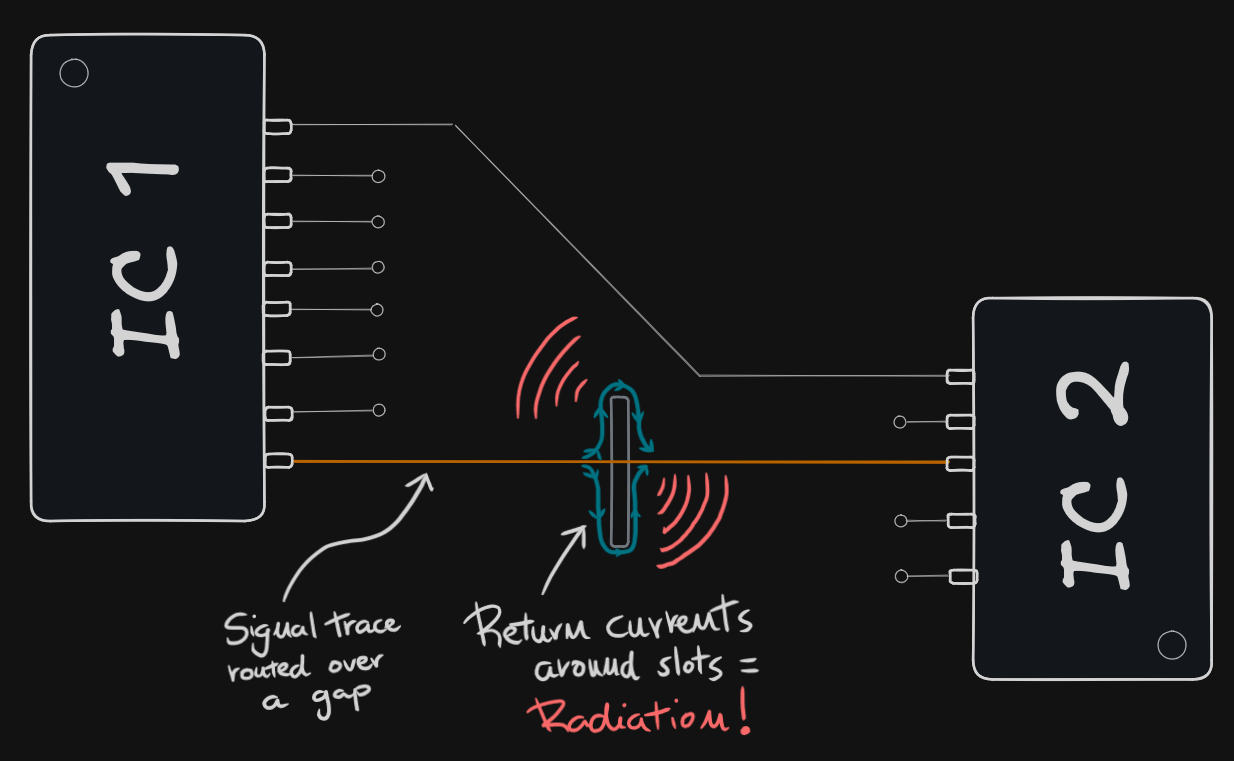

In the diagram, we have a high speed signal trace over a gap that goes from IC1 to IC2.

If we look at the currents around the slot:

We see that the gap will have the DC/low frequency currents (blue) or conduction currents going around it or the path of least resistance. The high frequency currents (red) will flow through the least impedance path which in this case will be across the gap, potentially radiating a fraction of it away.

Simulation Time

Now for the fun stuff. I’ve setup two simulation models, one with a solid return path and another one with a slot underneath the trace:

Here’s the two return planes:

I’ve applied a clock signal to make sure there is plenty of harmonics and this is the simulated emissions (E-field) at 10 cm from the trace, just above it:

Even for a 1 mm by 1 mm small gap, the emissions are 5-6 dB higher for the fundamental and all of its harmonics.

You could say that 5-6 dB doesn’t seem that much different but 6 dB when talking about E/H fields is double the amount of emissions.

Let’s look at the electric field distribution around the slot:

Blue arrows are low electric field and red arrows are high electric field. Clearly, around the slot we have a much higher electric field.

And here’s how the currents flow in the return plane with and without the gap:

Notice how the current stays below the trace when there is no gap, this will naturally be the path of least impedance.

When the gap is inserted, the current flows around its edges and it’s separated from the currents on the trace by the dimensions of the gap; congratulations, you just created a slot antenna!

Stitching the gap

Right, so now that we’ve seen that slots in your GND plane are evil, what can we do about it?

Obviously, avoiding gaps in the first place is the ideal solution but this is not always possible.

Another way is by placing a capacitor that bridges across the gap just underneath the trace. This is usually called a stitching capacitor.

A stitching capacitor is used to provide a lower impedance path to the currents passing across your gap, in a way that they will be less likely to radiate:

Let’s add a stitching cap to the previous simulation model and see if it improves emissions. I’ll go for a single, tiny one, 470 nF:

Look at that, just adding a small stitching cap, the emissions have gone down by about 4 dB.

Now, the model I’ve used in the simulation it’s an ideal lumped capacitor but in reality, your SMD capacitor is going to have some parasitics, like ESR (equivalent series resistance) and ESL (equivalent series inductance) which are going to screw the impedance of your capacitor.

Let’s add some realistic (kinda?) ESL and ESR, 0.5 nH and 15 mOhm respectively:

Yep, okay, as expected, the performance is not as good but still 2-3 dB of reduction compared to just having a big ol’ gap in your GND plane by itself.

No gaps, then?

As we have seen, a gap in your ground plane is likely to cause a lot of headcaches if you are not careful with your layout.

There is few situations where a gap on your ground plane is going to be (actually) required. If you can avoid them, please do.

The next best thing you can do is placing a stitching cap (or caps) across it with ideally low parasitics (low ESR/ESL) capacitors. You can find specific EMI suppression ones designed for stitching.

Also, don’t forget that when placing your stiching caps across the gap, there will be some even more parasitics due to the solder pads, so expected even worse performance than what I’ve showed in this post.

I hope this post dissuaded you from using GND plane gaps in your layout or at least you won’t lay a trace over them ever again!

Extra Resources

- The book “Electromagnetic Compatibility Engineering – 2nd Edition” by the late amazing Henry W. Ott, considered by many to be the EMC bible. Chapter 16 Section 3 covers return path discontinuities in much more detail.

- https://incompliancemag.com/slots-in-gnd-planes/ – A great technical article from Arturo Mediano, the EMI magician.

Leave a Reply